Strongest RISC-V Server Chip Released: 4nm and 192 Cores

Strongest RISC-V Server Chip Released: 4nm and 192 Cores, Outperforms AMD Epyc 9754

- Why Enterprise RAID Rebuilding Succeeds Where Consumer Arrays Fail?

- Linus Torvalds Rejects MMC Subsystem Updates for Linux 7.0: “Complete Garbage”

- The Man Who Maintained Sudo for 30 Years Now Struggles to Fund the Work That Powers Millions of Servers

- How Close Are Quantum Computers to Breaking RSA-2048?

- Why Windows 10 Users Are Flocking to Zorin OS 18 Instead of Linux Mint?

- How to Prevent Ransomware Infection Risks?

- What is the best alternative to Microsoft Office?

Strongest RISC-V Server Chip Released: 4nm and 192 Cores, Outperforms AMD Epyc 9754

November 9, 2023 – Ventana Micro Systems, a RISC-V server chip design company, unveiled its second-generation server CPU, the Veyron V2, during the 2023 RISC-V Summit.

The Veyron V2 brings comprehensive upgrades in various aspects, including instruction extensions, core design, interconnect standards, and manufacturing process.

The official claim is that it outperforms AMD’s high-end server chip, the Epyc 9754, making it the most powerful RISC-V server CPU to date. Additionally, Ventana offers customers the ability to incorporate custom accelerators into their System-on-Chip (SoC) blueprints.

Back in December 2022, Ventana released the world’s first server CPU based on the RISC-V architecture, the Veyron V1.

It employed a 5nm manufacturing process, featured Ventana’s high-performance RISC-V cores, an 8-stage pipeline design, out-of-order execution, clock speeds exceeding 3GHz, support for up to 16 cores per cluster, and up to 192 cores in a multi-cluster configuration.

The Veyron V1 also included 48MB of shared L3 cache, advanced side-channel attack mitigation, IOMMU, and advanced interrupt architecture (AIA), as well as comprehensive RAS features and top-down software performance tuning.

It claimed to outperform AMD EPYC 7763.

According to Ventana’s roadmap, the Veyron V1 was scheduled to launch in the second half of this year, but as of now, no customers have adopted it. This might be the reason why Ventana is eager to introduce the Veyron V2.

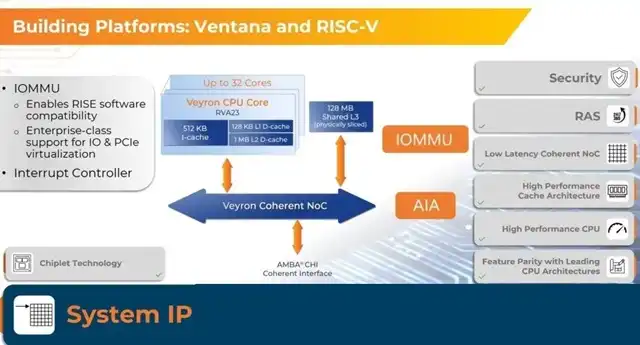

Travis Lanier, the Vice President of Marketing and Product at Ventana, explained that the all-new Veyron V2 incorporates all the updates from the RISC-V specification, such as the RVA23 feature set, which is the latest RISC-V instruction set architecture profile of this year, implementing the RISC-V Input-Output Memory Management Unit (IOMMU) specification. It also supports the Universal Chiplet Interconnect Express (UCIe) interconnect standard.

Lanier stated that the approval of the IOMMU specification is a significant development in the RISC-V domain, as it simplifies the process of accessing PCIe devices directly for virtual machine users, reducing software overhead and making it a crucial feature for data center applications.

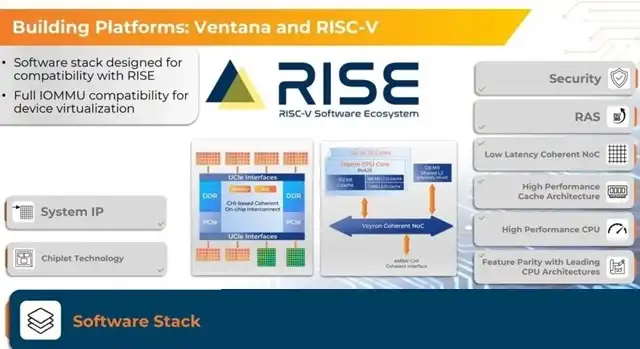

Veyron V2 also aims to be a compatibility design based on the RISC-V standard, making RISE (RISC-V Software Ecosystem) support crucial. Lanier further explained that RISE is an industry project aimed at building the necessary application ecosystem around RISC-V.

Ventana also added 512-bit vector processing units to its cores based on the RISC-V Vector Extension Specification and included AI matrix extension capabilities. Lanier claimed that this will significantly benefit certain AI or inference workloads.

Furthermore, support for DSA and the UCIe Chiplet standard enables faster chip manufacturing and allows customers to add FPGAs, ASIC accelerators, and more, increasing flexibility and reducing entry barriers for building software packages using smaller IP blocks with UCIe and I/O hubs.

Ventana’s co-founder and CEO, Balaji Baktha, also mentioned at the RISC-V Summit that Ventana’s customers can create potential CPU designs on the Veyron V2 using their intellectual property and other IP.

Regarding the core configuration of Veyron V2, it is based on a 4nm manufacturing process, retaining an 8-stage pipeline design, supporting out-of-order execution, with a maximum clock speed of 3.6GHz. The number of cores per cluster has been doubled to 32 compared to the previous generation, and in a multi-cluster setup, it can be expanded to a maximum of 192 cores. The cache size has been increased to 1MB per core for the L2 cache and 128MB for the shared cluster-level L3 cache.

Lanier stated that all these new upgrades in Veyron V2 result in nearly a 40% performance improvement compared to the previous generation. Official performance projections indicate that the 192-core Veyron V2 outperforms the AMD Epyc 9754, a high-end server chip.

Key upgrades in Veyron V2 include:

-

Interconnect Standard Transformation: Veyron V2 supports the UCIe (Universal Chiplet Interconnect Express) standard as a Chiplet (small chip) interconnect standard, as opposed to the previous Veyron V1’s BoW (Bunch of Wires) interface interconnect bus protocol. UCIe aims to provide an open and interoperable standard for connecting multiple silicon chips within a package.

-

Support for 512-bit Vector Extensions: Veyron V2 incorporates 512-bit vector extensions, similar to Intel’s AVX-512, enabling competitive performance in high-performance computing (HPC) and AI workloads.

-

New Core Architecture: Veyron V2 features an improved RISC-V core architecture that enhances instruction processing and overall performance. It supports the RVA23 architecture profile and is designed to run encryption functions on vector engines.

-

DSA Support: Veyron V2 supports DSA, enabling customers to add custom accelerator chips to their SoCs for specific workload optimizations.

-

Enhanced Security: Veyron V2 features comprehensive RAS capabilities, ECC support, and defense against side-channel attacks like Spectre and Meltdown.

The Veyron V2 is expected to enter production in the third quarter of 2024. Ventana will offer a 192-core 1U server reference design based on the Veyron V2 with four 128-core small chips and 12-channel DDR5-5600 memory. These small chips are interconnected using UCI Express, and an I/O interface allows them to be placed in server CPU slots.

In summary, Ventana’s Veyron V2 is poised to set new standards in the world of RISC-V server CPUs with its numerous enhancements and capabilities, promising superior performance, versatility, and security for data center applications.